# Precision Measurement Central (4)

## Part 4: RS485, or networking the MSCI2I0 micro

Design by J. Wickenhäuser

www.wickenhaeuser.com

The RS485 port on the MSC1210 board provides great opportunities for communication with other systems. For example, it allows a number of MSC1210 boards to be connected up into a network and talk to one another over distances of several kilometres.

This fourth instalment in the series on the MSC1210-based Precision Measurement Central (kicked off in the July/August 2003 issue) is entirely devoted to the RS485 interface. This month we will cover the theory and hardware. The December 2003 issue, finally, will discuss the practical use of the RS485 interface in a small project that goes to show how up to 255 MSC1210 boards can communicate with a single PC through an RS485 link. The converter required for the job is discussed in this article instalment.

## **RS485**

Although the RS485 interface has been around virtually since the earliest days of the PC era, it is rarely seen in real life, that is, on the PC's connector panel. That's why we take this opportunity to present a suitable converter for RS232 to RS485, which has been tailored for use in combination with the MSC1210 board. First, however, we need to wade though some theory.

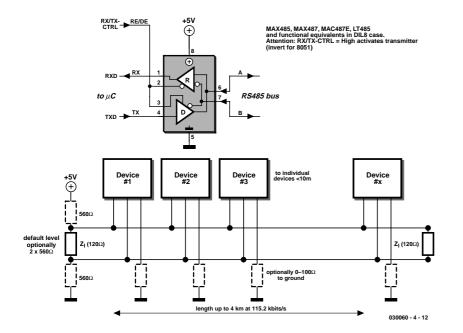

#### Bus topology

Normally an RS485 network consists of a long cable (bus) of which the ends are terminated with resistors. Up to 32 devices may be connected to the bus, or even 256 if a suitable driver chip is used. Ideally, all devices are connected to form a long thread. In practice, however, individual bus participants may also be connected via branches of several metres (**Figure 1**). In 'minimum' cases only

the two wires designated 'A' and 'B' are required, although it is recommended to implement potential cancellation using a third wire and an optional resistor. Another popular variant has four wires and allows the devices to be powered over the bus.

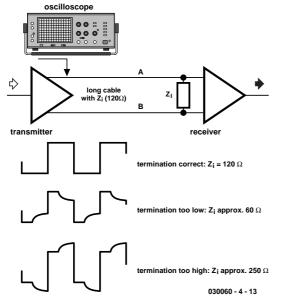

The digital information conveyed over the RS485 bus comprises the voltage difference between line 'A' and 'B'. If the difference is positive, the bus is said to convey a logic 1. In the other case, a logic 0 is conveyed. The use of differential voltages makes the bus rather immune to noise, provided a number of conditions are satisfied. **Figure 2** shows a bus with two devices on it, where the signal is to be carried from IN to OUT over a long cable. An oscilloscope is connected to the bus at the indicated position. Any cable will have a more or less distinctive impedance — values of 60 to 200  $\Omega$ being typical. The signal on the cable will remain undistorted only if the cable is terminated with a resistor whose value is approximately equal to the cable impedance. Wrong termination values cause signal distortion that can lead to data corruption and increased susceptibility of the bus to noise.

Fortunately, correct cable termination is really critical only in those cases where signals with a high data rate (> 57,600 bits/s) are conveyed over cable lengths exceeding

Elektor Electronics

Figure 1. RS485 topology.

500 m, when the propagation times start to approach the bit rates (the signal travels 100-300 m in 1  $\mu$ s). With cable lengths under 50 m and bit rates under 57,600, a cheap cable with no specified impedance but terminated with 120  $\Omega$  at both ends should be adequate.

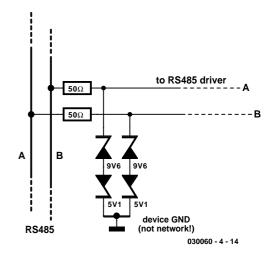

#### **Overvoltage Protection 'lite'**

An RS485 driver must be capable of withstanding line voltages between -7 V and +12 V at its input(s). Fair

enough, but longish cables in particular are prone to pick up (by induction) much higher peak voltages caused by electrostatic fields, discharges, EMI transients and so on. Consequently it makes sense to protect all RS485 against voltage surges. With suitable protection, short and not too powerful transients can not harm the drivers ICs (**Figure 3**).

#### Data traffic

The drawing in Figure 1 includes all

## **MICRO**CONTROLLER

optional resistors. These resistors serve to pull the bus to a fixed logic level when there is no traffic (that is, all devices are receiving and none is putting data on the bus). Unfortunately, this variant is rather wasteful in terms of energy usage and at the same time likely to cause problems with long cables.

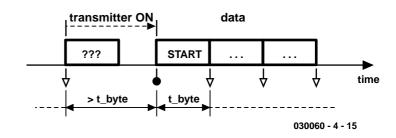

A better alternative is shown in **Figure 4**. In this configuration, the initial level of the bus is not known. If a device wants to put a data block on the bus, it has to activate its transmitter section first. However, as a result of improper termination as illustrated in Figure 2, it may happen that activation of the transmitter alone is sufficient for receiving devices on the bus to recognise data, when in fact no valid data has been sent as yet (see block marked ???).

This leads to the absolute requirement for a pause to be inserted immediately after activation of each transmitter section. This 'dead' period needs to be much longer than prescribed for the transmission of a single byte (t\_byte). The time needed to convey a byte over the bus is roughly ten times the reciprocal of the baud rate, or about 1 ms per byte when a rate of 9,600 bits/s is used.

The data packet proper always starts with a special marker byte (START). Note, however, that START may never occur within the actual data (more about this in the next instalment).

Because only one device can transmit at a time ('half duplex') a strict protocol is needed describing who's allowed to transmit what and when. If the protocol is not observed, data contention, collision and corruption is imminent. The practical application dis-

Figure 2. Why terminate?

Figure 3. Surge protection by means of two zener diodes.

## MICROCONTROLLER

cussed in next month's instalment employs a simple but effective protocol.

## A PC on the RS485 bus

If the two 560- $\Omega$  resistors shown in Figure 1 are used, the risk of 'undesired databytes' is greatly reduced. Problems may only occur with long cables (>50 m) and higher baud rates (>57,600 bits/s), particularly when the transmitting junction and the resistors are relatively far apart. Unfortunately, a PC can not exercise exact control over the pulse timing on its serial interface and so activate the transmitting device using an appropriate delay. After all, most PCs employ a UART (RS232 driver) with an internal transmitter FIFO. This prevents the PC from 'knowing' whether or not a databyte was actually sent or not. Consequently it is the task of the PC converter to ensure that the RS485 bus is at a valid logic level when there is no traffic.

## The converter

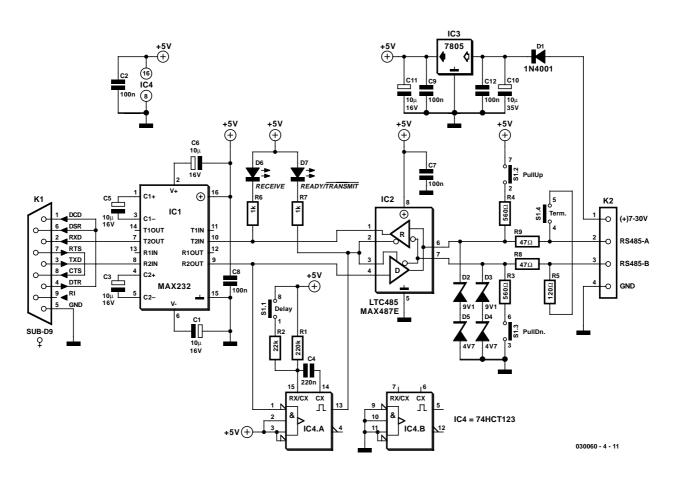

The converter, of which the circuit diagram is given in **Figure** 5, operates largely as a 'dumb' extension which has the benefit of it supporting different protocols and, of course,

Figure 4. Transmit timing.

bit rates. The design consists of an RS232 and an RS485 converter separated by good old TTL levels.

Bits arriving at the RS485 bus are copied directly to the PC irrespective of the bit rate. Once the PC sends a character, the converter immediately switches on its transmitter via a retriggerable monostable (IC1.A). The transmitter remains active for the time its takes to convey the byte. In the case of our circuit, two times may be selected: 20 ms for 1200 bits/s (S1 opened) or 2 ms for 9600 bits/s and higher (S1 closed).

In addition, switch S1.4 may be

used to include the terminator resistor, and/or S1.2/3 (operate at the same time) for the 560- $\Omega$  resistors to set the default level on the bus. These provisions on the converter allow several PCs or a combination of PCs and MSC1210 boards to be included in a network.

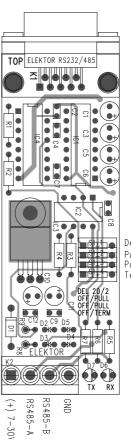

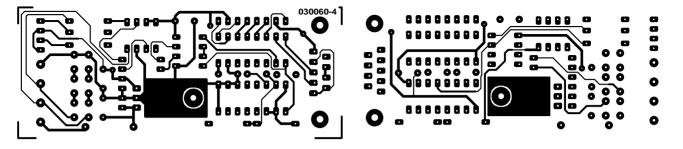

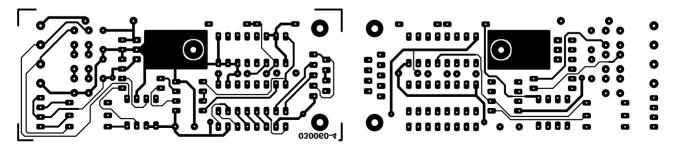

The construction of the converter on the printed circuit board shown in **Figure 6** should be an uncomplicated affair as there are no pitfalls with regard to soldering etc. The introductory photograph shows the author's prototype. The converter operates from an external supply voltage of

Figure 5. Circuit diagram of the RS232/RS485 converter.

## MICROCONTROLLER

## **COMPONENTS LIST**

#### **Resistors:**

$\begin{array}{l} {\sf RI} = 220 {\sf k} \Omega \\ {\sf R2} = 22 {\sf k} \Omega \\ {\sf R3}, {\sf R4} = 560 \Omega \\ {\sf R5} = 120 \Omega \\ {\sf R6}, {\sf R7} = 1 {\sf k} \Omega \\ {\sf R8}, {\sf R9} = 47 \Omega \end{array}$

#### **Capacitors:**

C1,C3,C5,C6,C11 =  $10\mu$ F 16V radial C2,C7,C8,C9,C12 = 100nF C4 = 220nF (10% tolerance) C10 =  $10\mu$ F 35V radial

#### Semiconductors:

DI = IN400I (DO4I case) D2,D3 = 9VI zener diode

between 7 V and 30 V and draws a modest 20 mA or so. In case the supply voltage is not obtained from the bus, the RS485 ground is connected to the circuit ground using a  $100-\Omega$  resistor for potential equalisation.

(030060-4)

D4,D5 = 4V7 zener diode

#### Miscellaneous:

K1 = 9-way sub-D socket, PCB mount, angled pins

K2 = 4-way PCB terminal block, 5mm lead pitch

S1 = 4-way DIL switch

Delay PullUp PullDw. Term.

Figure 6. PCB design for the RS232/RS485 converter.

non reflected

reflected

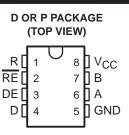

SLLS101B - JULY 1985 - REVISED JUNE 1999

- Bidirectional Transceivers

- Meet or Exceed the Requirements of ANSI Standards TIA/EIA-422-B and TIA/EIA-485-A and ITU Recommendations V.11 and X.27

- Designed for Multipoint Transmission on Long Bus Lines in Noisy Environments

- 3-State Driver and Receiver Outputs

- Individual Driver and Receiver Enables

- Wide Positive and Negative Input/Output Bus Voltage Ranges

- Driver Output Capability . . . ±60 mA Max

- Thermal Shutdown Protection

- Driver Positive and Negative Current Limiting

- Receiver Input Impedance . . . 12 kΩ Min

- Receiver Input Sensitivity . . . ±200 mV

- Receiver Input Hysteresis . . . 50 mV Typ

- Operate From Single 5-V Supply

#### description

The SN65176B and SN75176B differential bus transceivers are monolithic integrated circuits designed for bidirectional data communication on multipoint bus transmission lines. They are designed for balanced transmission lines and meet ANSI Standards TIA/EIA-422-B and TIA/EIA-485-A and ITU Recommendations V.11 and X.27.

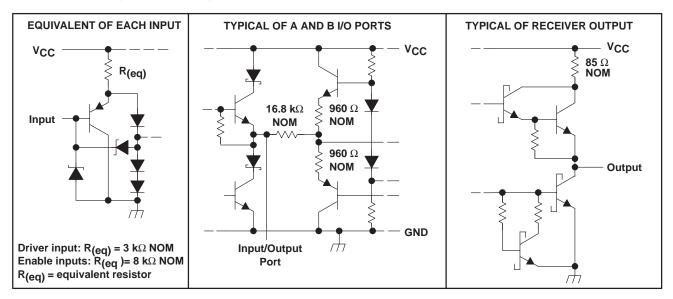

The SN65176B and SN75176B combine a 3-state differential line driver and a differential input line receiver, both of which operate from a single 5-V power supply. The driver and receiver have active-high and active-low enables, respectively, that can be connected together externally to function as a direction control. The driver differential outputs and the receiver differential inputs are connected internally to form differential input/output (I/O) bus ports that are designed to offer minimum loading to the bus when the driver is disabled or  $V_{CC} = 0$ . These ports feature wide positive and negative common-mode voltage ranges, making the device suitable for party-line applications.

The driver is designed for up to 60 mA of sink or source current. The driver features positive and negative current limiting and thermal shutdown for protection from line-fault conditions. Thermal shutdown is designed to occur at a junction temperature of approximately 150°C. The receiver features a minimum input impedance of 12 k $\Omega$ , an input sensitivity of ±200 mV, and a typical input hysteresis of 50 mV.

The SN65176B and SN75176B can be used in transmission-line applications employing the SN75172 and SN75174 quadruple differential line drivers and SN75173 and SN75175 quadruple differential line receivers.

The SN65176B is characterized for operation from  $-40^{\circ}$ C to  $105^{\circ}$ C and the SN75176B is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

#### SLLS101B - JULY 1985 - REVISED JUNE 1999

### **Function Tables**

| DD | IVE | D |

|----|-----|---|

|    |     | n |

| INPUT | ENABLE | OUTI | PUTS |

|-------|--------|------|------|

| D     | DE     | A B  |      |

| Н     | Н      | Н    | L    |

| L     | Н      | L    | Н    |

| Х     | L      | Z    | Z    |

| DIFFERENTIAL INPUTS<br>A–B                              | ENABLE<br>RE | OUTPUT<br>R |  |  |  |  |  |

|---------------------------------------------------------|--------------|-------------|--|--|--|--|--|

| $V_{ID} \ge 0.2 V$                                      | L            | Н           |  |  |  |  |  |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < 0.2 \text{ V}$ | L            | ?           |  |  |  |  |  |

| $V_{ID} \le -0.2 V$                                     | L            | L           |  |  |  |  |  |

| Х                                                       | н            | Z           |  |  |  |  |  |

| Open                                                    | L            | ?           |  |  |  |  |  |

H = high level, L = low level, ? = indeterminate, X = irrelevant, Z = high impedance (off)

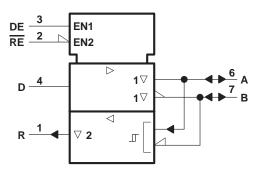

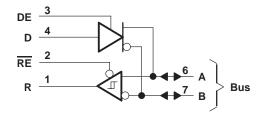

logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## logic diagram (positive logic)

SLLS101B - JULY 1985 - REVISED JUNE 1999

### schematics of inputs and outputs

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub> (see Note 1)                     |                        |

|------------------------------------------------------------------|------------------------|

| Voltage range at any bus terminal                                | $\ldots$ –10 V to 15 V |

| Enable input voltage, V <sub>I</sub>                             | 5.5 V                  |

| Package thermal impedance, $\theta_{JA}$ (see Note 2): D package | 197°C/W                |

| P package                                                        | 104°C/W                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds     | 260°C                  |

| Storage temperature range, T <sub>stg</sub>                      | . −65°C to 150°C       |

<sup>+</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential input/output bus voltage, are with respect to network ground terminal.

2. The package thermal impedance is calculated in accordance with JESD 51, except for through-hole packages, which use a trace length of zero.

#### MIN TYP MAX UNIT Supply voltage, V<sub>CC</sub> 4.75 5.25 5 V 12 Voltage at any bus terminal (separately or common mode), VI or VIC V -7 D, DE, and RE V High-level input voltage, VIH 2 D, DE, and RE V Low-level input voltage, VIL 0.8 V Differential input voltage, VID (see Note 3) ±12 Driver -60 mΑ High-level output current, IOH Receiver -400 μΑ Driver 60 Low-level output current, IOL mΑ 8 Receiver SN65176B -40 105 Operating free-air temperature, TA °C SN75176B 70 0

### recommended operating conditions

NOTE 3: Differential-input/output bus voltage is measured at the noninverting terminal A with respect to the inverting terminal B.

SLLS101B – JULY 1985 – REVISED JUNE 1999

## **DRIVER SECTION**

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                                           | TEST CON                | DITIONS <sup>†</sup>  | MIN                           | TYP‡ | MAX      | UNIT |

|-------------------|-----------------------------------------------------|-------------------------|-----------------------|-------------------------------|------|----------|------|

| VIK               | Input clamp voltage                                 | lı = – 18 mA            |                       |                               |      | -1.5     | V    |

| VO                | Output voltage                                      | IO = 0                  |                       | 0                             |      | 6        | V    |

| VOD1              | Differential output voltage                         | IO = 0                  |                       | 1.5                           | 3.6  | 6        | V    |

|                   | Differential output voltage                         | R <sub>L</sub> = 100 Ω, | See Figure 1          | 1/2 V <sub>OD1</sub><br>or 2¶ |      |          | V    |

|                   |                                                     | R <sub>L</sub> = 54 Ω,  | See Figure 1          | 1.5                           | 2.5  | 5        | V    |

| V <sub>OD3</sub>  | Differential output voltage                         | See Note 4              |                       | 1.5                           |      | 5        | V    |

| ∆ V <sub>OD</sub> | Change in magnitude of differential output voltage§ |                         |                       |                               |      | ±0.2     | V    |

| Voc               | Common-mode output voltage                          | $R_L$ = 54 Ω or 100 Ω,  | See Figure 1          |                               |      | +3<br>-1 | V    |

| ∆ Voc             | Change in magnitude of common-mode output voltage§  |                         |                       |                               |      | ±0.2     | V    |

| 10                | Output ourrest                                      | Output disabled,        | V <sub>O</sub> = 12 V |                               |      | 1        | mA   |

| 10                | Output current                                      | See Note 5              | $V_{O} = -7 V$        |                               |      | -0.8     | mA   |

| IIН               | High-level input current                            | VI = 2.4 V              |                       |                               |      | 20       | μA   |

| ۱ <sub>IL</sub>   | Low-level input current                             | VI = 0.4 V              |                       |                               |      | -400     | μA   |

|                   |                                                     | $V_{O} = -7 V$          |                       |                               |      | -250     |      |

|                   | Short-circuit output current                        | $V_{O} = 0$             | V <sub>O</sub> = 0    |                               |      | 150      | mA   |

| los               | Short-circuit output current                        | $A^{O} = A^{O}$         |                       |                               |      | 250      | IIIA |

|                   |                                                     | V <sub>O</sub> = 12 V   |                       |                               |      | 250      |      |

|                   | Supply current (total package)                      | No load                 | Outputs enabled       |                               | 42   | 70       | mA   |

| ICC               | Supply current (total package)                      | ino luau                | Outputs disabled      |                               | 26   | 35       | IIIA |

<sup>†</sup> The power-off measurement in ANSI Standard TIA/EIA-422-B applies to disabled outputs only and is not applied to combined inputs and outputs. <sup>‡</sup> All typical values are at  $V_{CC} = 5 V$  and  $T_A = 25^{\circ}$ C.

§ Δ|V<sub>OD</sub>| and Δ|V<sub>OC</sub>| are the changes in magnitude of V<sub>OD</sub> and V<sub>OC</sub>, respectively, that occur when the input is changed from a high level to a low level.

$\P$  The minimum V\_{OD2} with a 100- $\Omega$  load is either 1/2 V\_{OD1} or 2 V, whichever is greater.

NOTES: 4. See ANSI Standard TIA/EIA-485-A, Figure 3.5, Test Termination Measurement 2.

5. This applies for both power on and off; refer to ANSI Standard TIA/EIA-485-A for exact conditions. The TIA/EIA-422-B limit does not apply for a combined driver and receiver terminal.

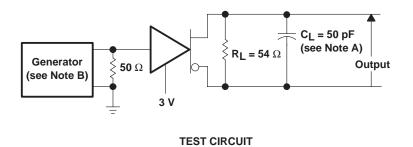

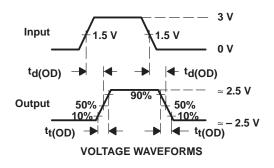

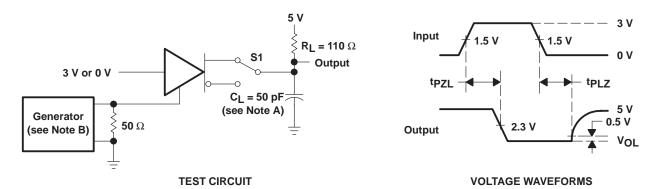

## switching characteristics, $V_{CC}$ = 5 V, $R_L$ = 110 k $\Omega$ , $T_A$ = 25°C (unless otherwise noted)

|                    |                                     |                                  |  |     |     | -   |      |

|--------------------|-------------------------------------|----------------------------------|--|-----|-----|-----|------|

|                    | PARAMETER                           | TEST CONDITIONS                  |  | MIN | TYP | MAX | UNIT |

| td(OD)             | Differential-output delay time      | $R_L = 54 \Omega$ , See Figure 3 |  |     | 15  | 22  | ns   |

| <sup>t</sup> t(OD) | Differential-output transition time |                                  |  | 20  | 30  | ns  |      |

| <sup>t</sup> PZH   | Output enable time to high level    | See Figure 4                     |  |     | 85  | 120 | ns   |

| t <sub>PZL</sub>   | Output enable time to low level     | See Figure 5                     |  |     | 40  | 60  | ns   |

| <sup>t</sup> PHZ   | Output disable time from high level | See Figure 4                     |  |     | 150 | 250 | ns   |

| <sup>t</sup> PLZ   | Output disable time from low level  | See Figure 5                     |  |     | 20  | 30  | ns   |

SLLS101B - JULY 1985 - REVISED JUNE 1999

| SYMBOL EQUIVALENTS   |                                         |                                                    |  |  |  |  |  |

|----------------------|-----------------------------------------|----------------------------------------------------|--|--|--|--|--|

| DATA-SHEET PARAMETER | TIA/EIA-422-B                           | TIA/EIA-485-A                                      |  |  |  |  |  |

| VO                   | V <sub>oa,</sub> V <sub>ob</sub>        | V <sub>oa,</sub> V <sub>ob</sub>                   |  |  |  |  |  |

| IVOD1                | Vo                                      | Vo                                                 |  |  |  |  |  |

| IVOD2                | V <sub>t</sub> (R <sub>L</sub> = 100 Ω) | $V_t (R_L = 54 \Omega)$                            |  |  |  |  |  |

| Ινοd3Ι               |                                         | V <sub>t</sub> (Test Termination<br>Measurement 2) |  |  |  |  |  |

|                      | $  V_t  -  \overline{V}_t  $            | $   V_t -  \overline{V}_t   $                      |  |  |  |  |  |

| Voc                  | V <sub>OS</sub>                         | V <sub>os</sub>                                    |  |  |  |  |  |

|                      | $ V_{OS} - \overline{V}_{OS} $          | $ V_{OS} - \overline{V}_{OS} $                     |  |  |  |  |  |

| IOS                  | I <sub>sa</sub>  ,  I <sub>sb</sub>     |                                                    |  |  |  |  |  |

| lo                   | I <sub>xa</sub>  ,  I <sub>xb</sub>     | l <sub>ia</sub> , l <sub>ib</sub>                  |  |  |  |  |  |

## **RECEIVER SECTION**

electrical characteristics over recommended ranges of common-mode input voltage, supply voltage, and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                              | TEST CO                                     | ONDITIONS                  | MIN   | TYP <sup>†</sup> | MAX  | UNIT |

|------------------|----------------------------------------|---------------------------------------------|----------------------------|-------|------------------|------|------|

| VIT+             | Positive-going input threshold voltage | V <sub>O</sub> = 2.7 V,                     | $I_{O} = -0.4 \text{ mA}$  |       |                  | 0.2  | V    |

| VIT-             | Negative-going input threshold voltage | V <sub>O</sub> = 0.5 V,                     | I <sub>O</sub> = 8 mA      | -0.2‡ |                  |      | V    |

| V <sub>hys</sub> | Input hysteresis voltage (VIT+-VIT-)   |                                             |                            |       | 50               |      | mV   |

| VIK              | Enable Input clamp voltage             | lı = -18 mA                                 |                            |       |                  | -1.5 | V    |

| Vон              | High-level output voltage              | V <sub>ID</sub> = 200 mV,<br>See Figure 2   | I <sub>OH</sub> = -400 μA, | 2.7   |                  |      | V    |

| VOL              | Low-level output voltage               | $V_{ID} = -200 \text{ mV},$<br>See Figure 2 | I <sub>OL</sub> = 8 mA,    |       |                  | 0.45 | V    |

| loz              | High-impedance-state output current    | $V_{O} = 0.4 \text{ V to } 2.4 \text{ V}$   |                            |       |                  | ±20  | μA   |

|                  |                                        | Other input = 0 V,                          | VI = 12 V                  |       |                  | 1    | mA   |

| 1                | Line input current                     | See Note 6                                  | $V_{I} = -7 V$             |       |                  | -0.8 | ША   |

| ЧΗ               | High-level enable input current        | VIH = 2.7 V                                 |                            |       |                  | 20   | μA   |

| ΙL               | Low-level enable input current         | V <sub>IL</sub> = 0.4 V                     |                            |       |                  | -100 | μA   |

| rı               | Input resistance                       | V <sub>I</sub> = 12 V                       |                            | 12    |                  |      | kΩ   |

| los              | Short-circuit output current           |                                             |                            | -15   |                  | -85  | mA   |

|                  | Supply surrent (total paskage)         | No load                                     | Outputs enabled            |       | 42               | 55   | m۸   |

| ICC              | Supply current (total package)         | INU IUAU                                    | Outputs disabled           |       | 26               | 35   | mA   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> The algebraic convention, in which the less positive (more negative) limit is designated minimum, is used in this data sheet for common-mode input voltage and threshold voltage levels only.

NOTE 6: This applies for both power on and power off. Refer to EIA Standard TIA/EIA-485-A for exact conditions.

SLLS101B – JULY 1985 – REVISED JUNE 1999

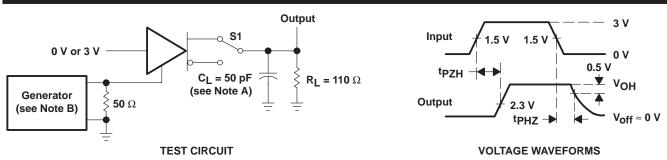

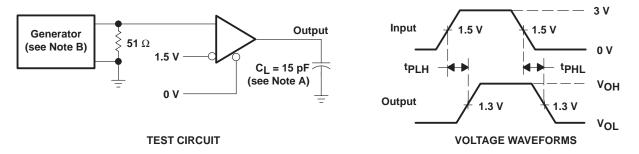

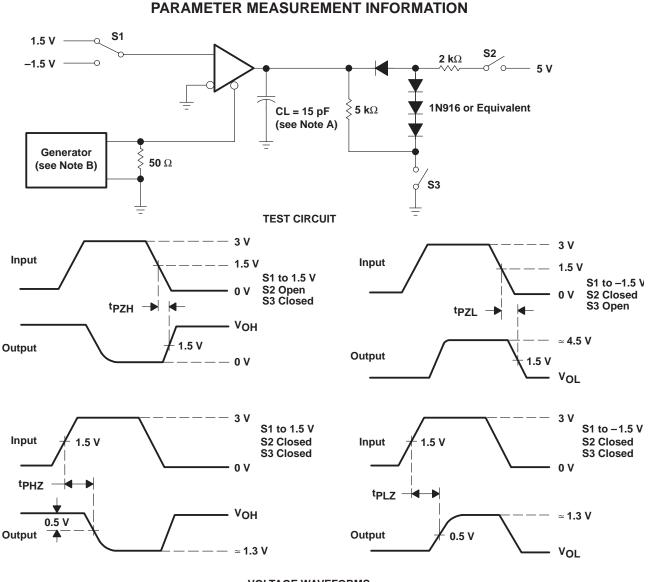

## switching characteristics, V<sub>CC</sub> = 5 V, C<sub>L</sub> = 15 pF, T<sub>A</sub> = 25°C

|                  | PARAMETER                                         | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------------------|-----------------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output |                                   |     | 21  | 35  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output | $V_{ID} = 0$ to 3 V, See Figure 6 |     | 23  | 35  | ns   |

| <sup>t</sup> PZH | Output enable time to high level                  | Soo Eiguro 7                      |     | 10  | 20  | ns   |

| t <sub>PZL</sub> | Output enable time to low level                   | See Figure 7                      |     | 12  | 20  | ns   |

| <sup>t</sup> PHZ | Output disable time from high level               | See Figure 7                      |     | 20  | 35  | ns   |

| <sup>t</sup> PLZ | Output disable time from low level                | See Figure 7                      |     | 17  | 25  | ns   |

## PARAMETER MEASUREMENT INFORMATION

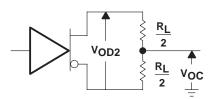

Figure 1. Driver  $V_{OD}$  and  $V_{OC}$

Figure 2. Receiver VOH and VOL

NOTES: A.  $C_{\mbox{L}}$  includes probe and jig capacitance.

B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

## Figure 3. Driver Test Circuit and Voltage Waveforms

SLLS101B - JULY 1985 - REVISED JUNE 1999

- NOTES: A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>Q</sub> = 50  $\Omega$ .

#### Figure 4. Driver Test Circuit and Voltage Waveforms

- NOTES: A. C<sub>1</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

#### Figure 5. Driver Test Circuit and Voltage Waveforms

- NOTES: A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  8 ns, t<sub>f</sub>  $\leq$  8

### Figure 6. Receiver Test Circuit and Voltage Waveforms

SLLS101B – JULY 1985 – REVISED JUNE 1999

**VOLTAGE WAVEFORMS**

NOTES: A. CL includes probe and jig capacitance.

B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>r</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  8 ns, t<sub>f</sub>  $\leq$  8

### Figure 7. Receiver Test Circuit and Voltage Waveforms

SLLS101B - JULY 1985 - REVISED JUNE 1999

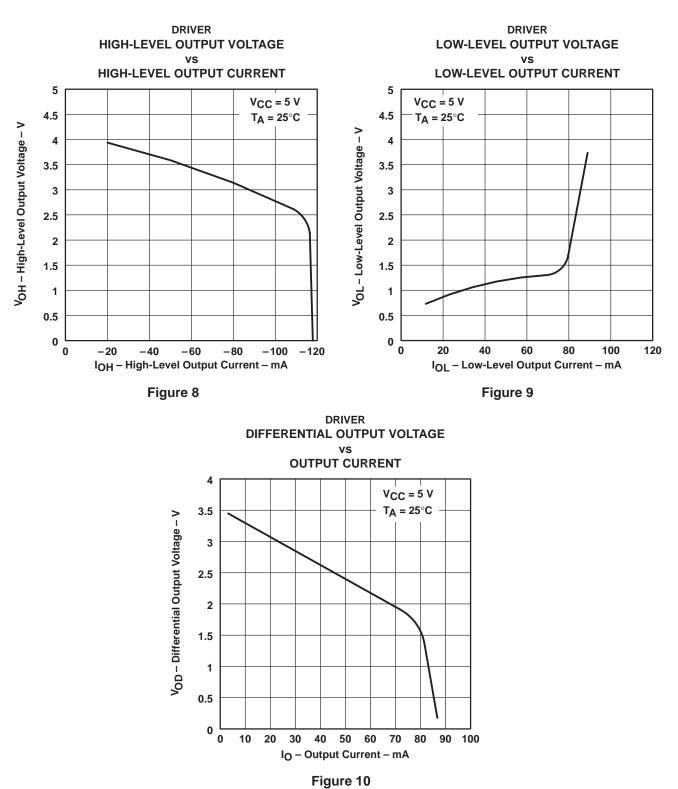

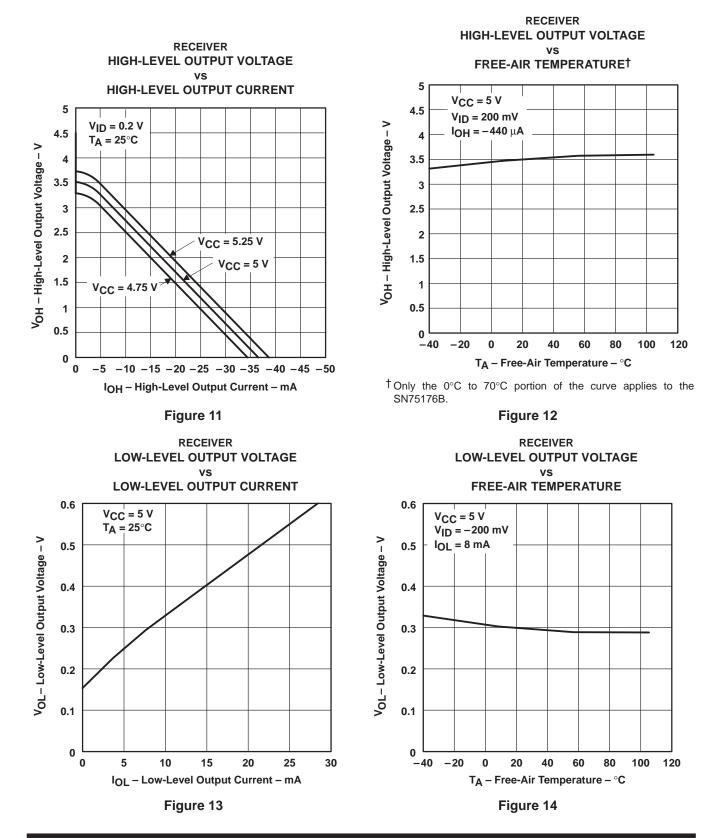

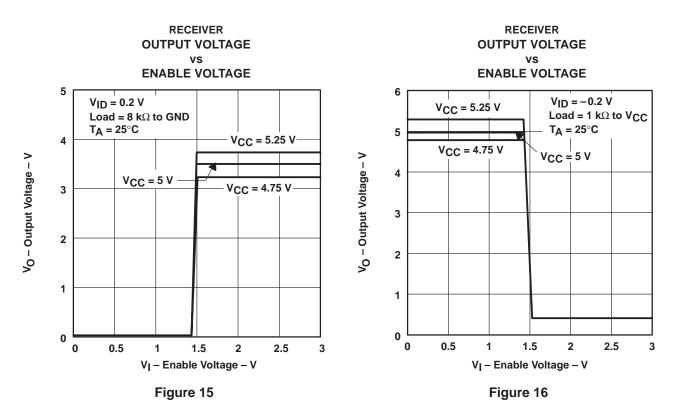

## **TYPICAL CHARACTERISTICS**

SLLS101B – JULY 1985 – REVISED JUNE 1999

## **TYPICAL CHARACTERISTICS**

SLLS101B - JULY 1985 - REVISED JUNE 1999

## **TYPICAL CHARACTERISTICS**

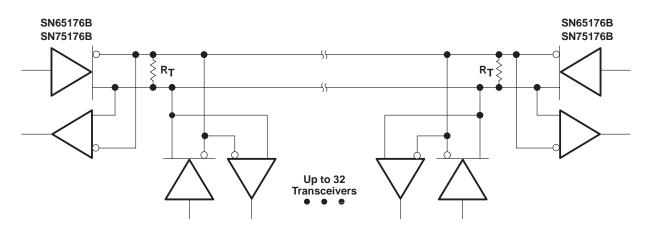

**APPLICATION INFORMATION**

NOTE A: The line should be terminated at both ends in its characteristic impedance (R<sub>T</sub> = Z<sub>O</sub>). Stub lengths off the main line should be kept as short as possible.

Figure 17. Typical Application Circuit

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated